# NOTICE WARNING CONCERNING COPYRIGHT RESTRICTIONS:

The copyright law of the United States (title 17, U.S. Code) governs the making of photocopies or other reproductions of copyrighted material. Any copying of this document without permission of its author may be prohibited by law.

CMU-CS-80-111

# Statistics on VLSI Designs<sup>1</sup>

Jon Louis Bentley<sup>2</sup> Dorothea Haken Robert W. Hon

Department of Computer Science Carnegie-Mellon University Pittsburgh, Pennsylvania 15213

## 17 April 1980

Abstract -- This paper presents a statistical study of the components on VLSI chips. We examine the size and shape of components, and their placement over the chip area. The data is useful for building efficient VLSI design tools: the form of the distribution shows that some simple strategies can lead to efficient algorithms, and the parameters of the distribution aid in choosing program parameters. To illustrate the application of the statistics to VLSI design tasks, we present an algorithm for solving the "rectangle intersection" problem that arises in design rule checkers.

<sup>&</sup>lt;sup>1</sup>This research was supported in part by the Defense Advanced Research Projects Agency under Contract F33615-78-C-1551 (monitored by the Air Force Office of Scientific Research) and in part by the Office of Naval Research under Contract N00014-76-C-0370.

<sup>&</sup>lt;sup>2</sup>Also with the Department of Mathematics.

|                                                                                                                                                                                              | Table of Contents                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 1. Introduction                                                                                                                                                                              |                                                          |

| 2. Statistics on Designs                                                                                                                                                                     | 5                                                        |

| 2.1 Description of the I<br>2.2 Statistics on Shape<br>2.2.1 A Trichotom<br>2.2.2 Data on Cor<br>2.2.3 Data on Wire<br>2.2.4 Data on Oth<br>2.3 Data on Placement<br>2.4 A Probabilistic Mod | e<br>ny of Rećtangles<br>nponents<br>es<br>er Rectangles |

| 3. Applications of the S                                                                                                                                                                     | tatistics                                                |

| 3.1 An Algorithm for Fi<br>3.2 A Pascal Program<br>3.3 Applications in VLS                                                                                                                   | nding Rectangle Intersections                            |

| 4. Conclusions                                                                                                                                                                               |                                                          |

| References                                                                                                                                                                                   |                                                          |

| I. Description of the Ch                                                                                                                                                                     | ips                                                      |

| II. Component Histogra                                                                                                                                                                       | ms                                                       |

| III. Wire Histograms                                                                                                                                                                         |                                                          |

| IV. Histograms of Other                                                                                                                                                                      | Rectangles                                               |

| V. Placement Histograr                                                                                                                                                                       | ns                                                       |

| V.1 Two-dimensional H<br>V.2 One-dimensional H                                                                                                                                               | -                                                        |

| VI. Data on Rectangle A                                                                                                                                                                      | rea                                                      |

.

### VLSI Statistics

# 1. Introduction

The "VLSI explosion" seems to be making the world of computers better and better: with every technological advance we can build machines that are smaller, faster, and cheaper than their predecessors. There are, however, several concomitant difficulties associated with these advances, one of the more noticeable being the problems inherent in designing a chip that contains hundreds of thousands of transistors. For this reason a great deal of recent research has focussed on building a VLSI design system that can automate certain design tasks. These tasks include such problems as *laying out* components, *routing* wires between components, and *design rule checking* to ensure that the design satisfies a set of constraints.

The primary purpose of this paper is to present a set of statistics on VLSI chips that can be used when constructing a VLSI design system. The statistics describe the geometry of chips: that is, the shape of their components and how those components are placed on the chip. To illustrate the application of the statistics, we will describe an algorithm useful in design rule checking that was developed by using the statistics. (A design rule checker that uses this algorithm is currently under development at Carnegie-Mellon.) The primary audience for this paper, therefore, is the community interested in constructing VLSI design systems.

A secondary purpose of this paper is to provide a study in "applied algorithm design". A great deal of work has been done recently on the probabilistic analysis of algorithms, and the design of algorithms with fast expected running time. One weak part of that work, however, is that it has merely assumed that the input data is drawn from a particular underlying distribution, and has not questioned how practitioners might justify that assumption. This paper provides an example of the justification of probabilistic assumptions, and the development of both an abstract algorithm and a concrete program based on the assumptions.

Chapter 2 contains the statistical study of a set of VLSI designs. An algorithm for computing rectangle intersections that exploits those statistics to achieve fast expected running time is presented in Chapter 3, and conclusions are offered in Chapter 4.

#### VLSI Statistics

# 2. Statistics on Designs

In this chapter we will study the distribution of components on VLSI chips. There are two primary knowledge sources that we will bring to bear in this study. The first is an *a priori* knowledge of the design style of (at least one school of) chip designers. The second source is an empirical study of a set of actual chip designs.

This chapter is organized as follows. In Section 2.1 we briefly describe both the basic design philosophy underlying the chips we studied and the chips themselves. Section 2.2 contains statistics on the *shape* of the components placed on chips, and Section 2.3 contains statistics on the *placement* of the components on the chips. A probabilistic model summarizing these studies is presented in Section 2.4. (All the measurements in this chapter are used in the construction of the rectangle intersection algorithm described in Chapter 3. Since issues of area are not important for the algorithm of Chapter 3, we defer discussion of the data on the area occupied by components and wires to Appendix VI.)

# 2.1 Description of the Designs

Before we describe the statistics in detail, it is important to give a few words of background on the chip designs studied. All were the result of VLSI design courses taught at research institutions, including Caltech, Carnegie-Mellon, MIT, Stanford, and Xerox PARC. The designers were researchers schooled in the Mead and Conway [1980] style of hierarchical IC design; the target process was silicon-gate nMCS, using Mead and Conway's design rules and a value of  $\lambda$  from 2.0 to 3.0 microns. (The constant  $\lambda$  is the size of the smallest features resolvable by the implementation process; typical minimum-sized transistors have gate widths of  $2\lambda$ .) All of the designs were expressed in a geometric specification language called *Caltech Intermediate Format* (or CIF – see Hon and Sequin [1980]), regardless of the design system used to lay out the chip.

In this section we will present statistics on sixteen VLSI designs. All designs are taken from recent multiproject chips managed by the LSI group at Xerox PARC. Communication and file transfer were facilitated by the ARPANET. The sixteen chips we study are all those available to us that contain over ten thousand geometric primitives. The designs were for a variety of tasks, ranging from a digital clock to a machine that interprets Lisp code; a short description of the sixteen chips is available in Appendix I. In addition to the tables in this chapter summarizing the sixteen chips, the six largest chips are examined in more detail in Appendices II through V.

The results that we will present in this chapter are drawn from a relatively small number of designs, yet we feel that they are applicable in a much broader context. We will now enumerate several issues regarding the chips chosen for our study, and discuss how those issues affect the scope of our

conclusions.

- The designs are fairly small. Although all designs consisted of at least 10,000 rectangles, the largest had only 109,862 rectangles.<sup>3</sup> Our results are quite consistent across this order-of-magnitude difference, and we see no reason to believe that they will change significantly for larger chips.

- All designs were in the Mead-Conway style. This implies that the designers placed emphasis on regular, modular designs with clean communication schemes, rather than optimizing the circuit for the densest (in terms of active devices per  $\lambda^2$  area) layout. This is a fundamental departure from common industrial practice.

- Are the results biased towards a particular design system? The CIF descriptions we processed were produced by a variety of design systems, ranging from an interactive drawing system to a simple version of a "silicon compiler." For this reason, we expect the set of designs to be free of heavy bias from one particular design system. It should be noted that many cells used in the designs came from a common library (for example, input/output pads and PLA cells).

- Our studies ignored the hierarchy inherent in CIF. Our study of the chips dealt only with the instantiated symbols on the chip, ignoring the hierarchical structure of their CIF descriptions.

- Logos on the chips were not excluded from our study. Several of the chips we studied contain pictures, ranging in complexity from the designer's initials to a map of the Boston subway system. The components in these logos were included in our studies as though they were active components in the design. Because there were relatively few logos, and all contain relatively few rectangles, the logos had little impact on our statistics.

## 2.2 Statistics on Shape

The first set of statistics we gathered has to do with the *shape* of the components on chips. All of the chips we examined were designed using primarily rectangles with edges parallel to the coordinate axes. The few components that were not rectangles were surrounded by their "bounding rectangles" before being passed to our analysis programs. We may therefore refer to the chip components as rectangles, and the task of this section is to describe the shapes of the rectangles on the chips. In Section 2.2.1 we introduce a trichotomy that places each rectangle in one of three distinct classes, and the rectangles within these classes are then studied in Sections 2.2.2, 2.2.3 and 2.2.4, respectively.

- 3 -

<sup>&</sup>lt;sup>3</sup>To relate the rectangle count to the more typical measure of active device count, we note that chip 15 had approximately 96,000 rectangles and 13,500 active devices, while chip 16 had approximately 110,000 rectangles and 11,000 active devices.

## 2.2.1 A Trichotomy of Rectangles

Any attempt to describe homogeneously all rectangles on a VLSI chip is doomed to failure. No matter what measurements are chosen (such as average edge length, aspect ratio, or area), there will be a tremendous variance in the results. The reason for this variance is that designers use several fundamentally different classes of rectangles, and although the rectangles within these classes are quite similar, rectangles across the classes are remarkably different. As a first approximation, it is safe to say that most designers have the following classes of rectangles in mind as they design a VLSI circuit: *components* -- the small rectangles used to synthesize logic or storage devices; *wires* -- the skinny rectangles used to connect distant components; and *other* rectangles (for example, large pads).

To formalize our intuitive notions, we gave these fuzzy concepts the following precise definitions.

- A component is any rectangle with neither side greater than 10λ.

- A wire is a rectangle with one side greater than  $10\lambda$  and the other side not greater than  $6\lambda$ .

- An other rectangle is any rectangle that is neither a component nor a wire.

It is important to emphasize that a rectangle classified as a wire, for instance, in the above trichotomy is not necessarily viewed as such by the designer<sup>4</sup>; nonetheless, this trichotomy will serve well in explaining the various shapes on chips. The robustness of this trichotomy is substantiated both by the consistency of the data soon to be presented, and by the histograms of Appendices II and IV. (Discussions of the robustness can be found in those appendices.)

Table 1 contains the first set of data we gathered; we will explain the various columns of the table by describing in detail its first row. That row describes chip number 1, which contains 10803 rectangles. Of those rectangles, 6723 (or 62.2%) are classified as components. Additionally, 1665 rectangles are vertical wires and 2002 are horizontal wires; therefore a total of 33.9% of all rectangles are wires (either vertical or horizontal). The remaining 413 rectangles were classified as "others", for a total of 3.8% of all rectangles. The last three columns of the table report data on all 21606 edges of the rectangles (note the number of edges on a chip is twice the number of rectangles). The mean edge length is 8.8 $\lambda$ , with a standard deviation of 18.6 $\lambda$ , and the longest edge on the chip is 660 $\lambda$ .

<sup>&</sup>lt;sup>4</sup>Likewise, what is viewed as a wire by the designer may be classified by this trichotomy as many components. This is because long data paths may be built up out of many pieces in hierarchical designs. For example, if a memory array is constructed by a sequence of instantiations of a symbol defining a single memory cell, then each cell would contain a piece of the data line running through the entire array. The measurements under discussion are based on the rectangles that result from the fully instantiated symbol structure. No effort was made to coalesce separate pieces of the same wire. Atthough an analysis of the "coalesced" structure is also interesting, we present our results because many programs that work with chip designs are given input in this form.

**VLSI Statistics**

| Chip | #      | Compo | nents |      | Wires    |      |      | ers | Edg  | Edge Length |               |

|------|--------|-------|-------|------|----------|------|------|-----|------|-------------|---------------|

| #    | Rects  | #     | %     | # Ve | rt # Hor | %    | #    | %   | Меал | S. D.       | Max           |

| 1    | 10803  | 6723  | 62.2  | 1665 | 2002     | 33.9 | 413  | 3.8 | 8.8  | 18.6        | 660           |

| 2    | 11265  | 8409  | 74.6  | 1356 |          | 23.0 | 265  | 2.4 | 7.9  | 39.3        | 1711          |

| 3    | 11566  | 8491  | 73.4  | 1164 |          | 25.1 | 174  | 1.5 | 7.9  | 18.7        | 800           |

| 4    | 11853  | 7733  | 65.2  | 1826 | 1914     | 31.5 | 380  | 3.2 | 8.5  | 22.5        | 1088          |

| 5    | 11915  | 9027  | 75.8  | 1277 | 1356     | 22.1 | 255  | 2.1 | 7.5  | 23.0        | 954           |

| 6    | 12063  | 7405  | 61.4  | 2324 | 2149     | 37.1 | 185  | 1.5 | 8.0  | 22.6        | 909           |

| 7    | 12800  | 9176  | 71.7  | 1605 | 1744     | 26.1 | 275  | 2.1 | 7.6  | 14.4        | 406           |

| 8    | 14186  | 10936 | 77.1  | 920  | 2076     | 21.1 | 254  | 1.8 | 8.6  | 36.8        | 1155          |

| 9    | 14423  | 11324 | 78.5  | 1189 | 1611     | 19.4 | 299  | 2.1 | 6.3  | 10.1        | 106           |

| 10   | 15097  | 10786 | 71.4  | 2012 | 2015     | 26.6 | 284  | 1.9 | 6.9  | 11.6        | 356           |

| 11   | 16194  | 11128 | 68.7  | 2565 | 2103     | 28.8 | 398  | 2.5 | 8.9  | 22.6        | 9 <b>68</b> . |

| 12   | 17565  | 10219 | 58.2  | 3598 | 3124     | 38.3 | 624  | 3.6 | 6.7  | 9.5         | 460           |

| 13   | 18056  | 13731 | 76.0  | 2381 | 1751     | 22.9 | 193  | 1.1 | 7.0  | 16.2        | 1068          |

| 14   | 33387  | 25431 | 76.2  | 3078 | 4628     | 23.1 | 250  | 0.7 | 6.8  | 18.1        | 1675          |

| 15   | 95901  | 76116 | 79.4  | 6773 | 12108    | 19.7 | 904  | 0.9 | 6.7  | 18.7        | 2902          |

| 16   | 109682 | 73939 | 67.4  | 1783 | 3 16874  | 31.7 | 1031 | 0.9 | 7.0  | 21.9        | 1523          |

#### Table 1. General data on rectangles.

The percentages in Table 1 show that our trichotomy of rectangles is consistent with chip designs -- that is, the percentages of components, wires and others remain approximately constant across various chips. This can be seen roughly by scanning the fourth, seventh, and ninth columns of Table 1. To make the comparison more obvious, we offer the following summary of those columns of Table 1.

|              | Median | Mean | S.D. |

|--------------|--------|------|------|

| % Components | 72.5   | 71.1 | 6.34 |

| % Wires      | 25.6   | 26.9 | 5.84 |

| % Others     | 2.0    | 2.0  | .91  |

\_ \_

That is, of the sixteen component percentages, the median is 72.5%, the mean is 71.1% and the standard deviation is 6.3%. This summary shows that all three percentages remain consistent across the sixteen chips: the median and the mean percentages are very close, and the standard deviations are fairly small.

The second interesting aspect of Table 1 is contained in the last three columns, which summarize the edge lengths observed on the chip. Note that the mean edge length observed is very consistent: the mean of the sixteen values is  $7.57\lambda$ , while the median is  $7.55\lambda$ . Unfortunately, the standard deviation of edge lengths is also consistent -- consistently very high. The median standard deviation is  $18.7\lambda$  and the mean is  $20.3\lambda$ . The high standard deviations are due to the fact that there is a tremendous discrepancy among different kinds of rectangles; to reduce this deviation we must study rectangles in the various classes individually.

- 5 -

### 2.2.2 Data on Components

The data in Table 2 describes the rectangles that were classified as components (that is, those rectangles with neither edge greater than  $10\lambda$ ). The first four columns repeat information from Table 1; the fifth column reports the mean edge length of all components on the chip (in  $\lambda$ ), and the sixth reports the standard deviation of the edge lengths. The edge lengths are remarkably consistent: the median of the sixteen averages is  $3.9\lambda$ , and their mean is also  $3.9\lambda$  (with a standard deviation of only .16 $\lambda$ ). Note that the standard deviations are all very close to  $2\lambda$ .

| Chip | #      | Compo | onents | Edge Length |       |  |  |

|------|--------|-------|--------|-------------|-------|--|--|

| #    | Rects  | #     | %      | Mean        | S. D. |  |  |

|      |        |       |        |             |       |  |  |

| 1    | 10803  | 6723  | 62.2   | 3.9         | 2.0   |  |  |

| 2    | 11265  | 8409  | 74.6   | 3.8         | 1.9   |  |  |

| 3    | 11566  | 8491  | 73.4   | 4.2         | 2.3   |  |  |

| 4    | 11853  | 7733  | 65.2   | 4.0         | 2.1   |  |  |

| 5    | 11915  | 9027  | 75.8   | 3.6         | 1.9   |  |  |

| 6    | 12063  | 7405  | 61.4   | 3.9         | 2.0   |  |  |

| 7    | 12800  | 9176  | 71.7   | 3.9         | 2.0   |  |  |

| 8    | 14186  | 10936 | 77.1   | 3.9         | 1.9   |  |  |

| 9    | 14423  | 11324 | 78.5   | 3.8         | 1.6   |  |  |

| 10   | 15097  | 10786 | 71.4   | 3.9         | 2.0   |  |  |

| 11   | 16194  | 11128 | 68.7   | 4.0         | 2.0   |  |  |

| 12   | 17565  | 10219 | 58.2   | 3.5         | 1.6   |  |  |

| 13   | 18056  | 13731 | 76.0   | 3.9         | 1.8   |  |  |

| 14   | 33387  | 25431 | 76.2   | 3.7         | 2.0   |  |  |

| 15   | 95901  | 76116 | 79.4   | 4.0         | 2.1   |  |  |

| 16   | 109682 | 73939 | 67.4   | 3.8         | 1.7   |  |  |

Table 2. Data on components.

The above data is only a brief sketch of the distribution of components. More detailed studies are contained in Appendix II: we give two-dimensional histograms of component sizes for the six largest chips we studied. Those histograms show that the overwhelming majority of components on a chip are  $2\lambda$ -by- $2\lambda$ ,  $2\lambda$ -by- $4\lambda$ ,  $4\lambda$ -by- $4\lambda$ , or  $4\lambda$ -by- $6\lambda$  in size, which correspond to minimum-size contact cuts, polysilicon, diffusion, or metal flashes, and the contact cuts used in "butting contacts" (see Mead and Conway [1980]).

### 2.2.3 Data on Wires

Data on the rectangles that were classified as wires is contained in Table 3. The first five columns of that table are duplicated from Table 1. The next two columns describe the lengths of the short edges of the wires (which are, by definition, not greater than  $6\lambda$ ). The final three columns describe the lengths of the long edge of the wires (which are greater than  $10\lambda$ ).

VLSI Statistics

| Chip |        |        |       |      | Short | Edge  | Long Edge           |       | e    |

|------|--------|--------|-------|------|-------|-------|---------------------|-------|------|

| #    | Rects  | # Vert | # Hor | %    | Mean  | S. D. | Mean                | S. D. | Max  |

|      |        |        |       |      |       |       | <b>a</b> c <b>a</b> | 00.0  | 401  |

| 1    | 10803  | 1665   | 2002  | 33.9 | 3.1   | 1.3   | 25.6                | 28.3  | 461  |

| 2    | 11265  | 1356   | 1235  | 23.0 | 2.9   | 1.3   | 33.8                | 106.8 | 1711 |

| 3    | 11566  | 1164   | 1737  | 25.1 | 3.3   | 1.6   | 28.3                | 28.8  | 340  |

| 4    | 11853  | 1826   | 1914  | 31.5 | 3.1   | 1.1   | 24.8                | 34.6  | 488  |

| 5    | 11915  | 1277   | 1356  | 22.1 | 2.9   | 1.2   | 30.9                | 41.1  | 612  |

| 6    | 12063  | 2324   | 2149  | 37.1 | 3.2   | 1.0   | 23.4                | 39.7  | 630  |

| 7    | 12800  | 1605   | 1744  | 26.1 | 2.9   | 1.1   | 27.9                | 25.8  | 406  |

| 8    | 14186  | 920    | 2076  | 21.1 | 3.1   | 1.5   | 39.4                | 92.0  | 831  |

| 9    | 14423  | 1189   | 1611  | 19.4 | 3.2   | 1.5   | 23.5                | 17.0  | 96   |

| 10   | 15097  | 2012   | 2015  | 26.6 | 3.2   | 1.3   | 22.6                | 21.2  | 356  |

| 11   | 16194  | 2565   | 2103  | 28.8 | 3.0   | 1.2   | 32.1                | 40.5  | 791  |

| 12   | 17565  | 3598   | 3124  | 38.3 | 3.2   | 1.1   | 17.0                | 10.4  | 322  |

| 13   | 18056  | 2381   | 1751  | 22.9 | 3.2   | 1.4   | 26.8                | 23.5  | 303  |

| 14   | 33387  | 3078   | 4628  | 23.1 | 3.2   | 1.5   | 28.9                | 40.5  | 1284 |

| 15   | 95901  | 6773   | 12108 | 19.7 | 3.1   | 1.3   | 28.3                | 40.2  | 1771 |

| 16   | 109682 | 17838  | 16874 | 31.7 | 2.9   | 1.1   | 22.2                | 45.6  | 1523 |

#### Table 3. Data on wires.

A number of facts are apparent from Table 3. The first is that most designs have a number of horizontal wires approximately equal to the number of vertical wires, as one would expect. There are several designs, however, that are obviously not "balanced" in this sense: chips 3, 8, 14 and 15 all have at least 50% more horizontal wires than vertical.

The data concerning the short (not greater than  $6\lambda$ ) side of the wires is quite consistent. The mean of the sixteen mean values is  $3.1\lambda$  (with standard deviation  $.13\lambda$ ) and the median is  $3.1\lambda$ . The standard deviation of the short edge length is consistently very close to  $1.3\lambda$ .

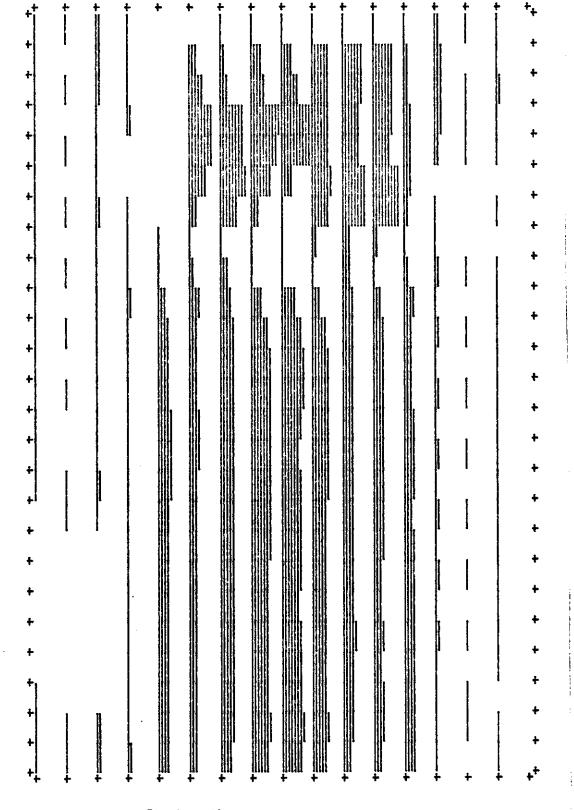

The lengths of the longer edge of the wires are more difficult to describe. The median value of the sixteen mean edge lengths is  $27.4\lambda$ , and their mean is  $27.2\lambda$  (with standard deviation of  $5.1\lambda$ ). The typical standard deviation is approximately  $40\lambda$ . Histograms of the distribution of the long edges can be found in Appendix III.

### 2.2.4 Data on Other Rectangles

Table 4 presents data on the "other" rectangles that were classified as neither components nor wires. The first four columns are duplicated from Table 1, and the last three columns describe the edge lengths of the components in  $\lambda$ .

The median of the sixteen average lengths is  $45\lambda$ ; their mean and standard deviation are  $43.1\lambda$  and  $8.5\lambda$ , respectively. The standard deviations are centered around  $80\lambda$ , but vary widely. Two-

-7-

| Chip | #      | Other | · Eo | dge Len | gth   |      |

|------|--------|-------|------|---------|-------|------|

| #    | Rects  | #     | %    | Mean    | S. D. | Max  |

|      |        |       |      |         |       |      |

| 1    | 10803  | 413   | 3.8  | 39.0    | 52.3  | 660  |

| 2    | 11265  | 265   | 2.4  | 35.7    | 71.8  | 1118 |

| 3    | 11566  | 174   | 1.5  | 53.7    | 98.6  | 800  |

| 4    | 11853  | 380   | 3.2  | 45.9    | 80.9  | 1088 |

| 5    | 11915  | 255   | 2.1  | 48.5    | 103.1 | 954  |

| 6    | 12063  | 185   | 1.5  | 45.7    | 95.0  | 909  |

| 7    | 12800  | 275   | 2.1  | 36.5    | 38.1  | 353  |

| 8    | 14186  | 254   | 1.8  | 57.6    | 128.2 | 1155 |

| 9    | 14423  | 299   | 2.1  | 37.2    | 29.2  | 106  |

| 10   | 15097  | 284   | 1.9  | 33.9    | 28.6  | 106  |

| 11   | 16194  | 398   | 2.5  | 44.3    | 75.8  | 968  |

| 12   | 17565  | 624   | 3.6  | 24.4    | 28.0  | 460  |

| 13   | 18056  | 193   | 1.1  | 56.1    | 104.9 | 1068 |

| 14   | 33387  | 250   | 0.7  | 46.1    | 88.5  | 1675 |

| 15   | 95901  | 904   | 0.9  | 38.2    | 114.5 | 2902 |

| 16   | 109682 | 1031  | 0.9  | 46.6    | 95.1  | 1416 |

Table 4. Data on "other" rectangles.

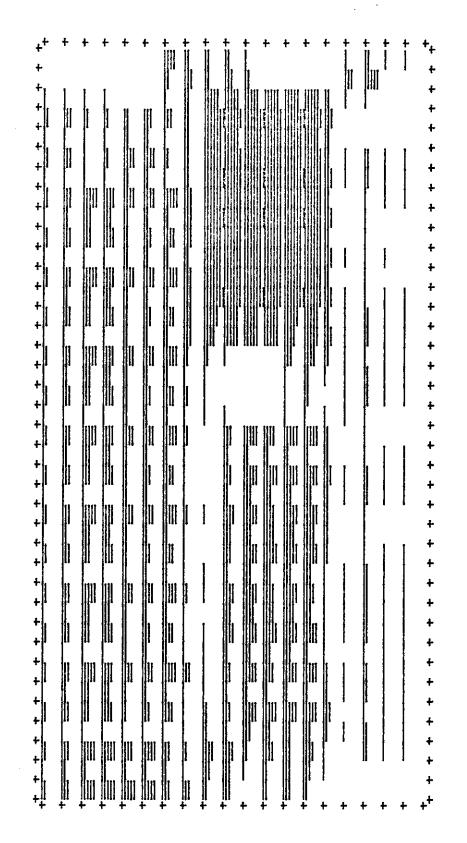

dimensional histograms showing the distributions of other components are available in Appendix IV.

## 2.3 Data on Placement

The data we have mentioned so far has discussed only the *shape* of the components; in this section we will describe how those shapes are distributed. There are two questions that we must answer in this study: in what sort of region are the rectangles placed, and how are they distributed over that region?

The first issue to be addressed is the region over which the rectangles are distributed. All the chips that we studied were designed to be enclosed within a bounding rectangle, referred to as its "bounding box". Table 5 contains data on the bounding boxes of the chips we studied. The first two columns are duplicated from Table 1. The next two columns give the width and the height of the chips' bounding boxes in  $\lambda$ . The fifth column of the table contains the aspect ratios of each chip, which is the ratio of the chip's longer dimension to its shorter dimension. The mean aspect ratio is 1.65, while the median is 1.31; the mean is larger than the median primarily because of the one "outlying" design with the aspect ratio of 4.57. This data allows us to conclude that most designs are approximately square.

Having investigated the aspect ratio of the bounding box, we must now study its size (as a function of the number of rectangles on the chip). To do this, the last column of Table 5 shows the ratio of the area of the bounding box (measured in  $\lambda^2$ ) to the number of the rectangles on the chip. Note that this

### VLSI Statistics

| Chip | #      | Chip | Bound | ling Box | Area (in $\lambda^2$ )/ |  |  |

|------|--------|------|-------|----------|-------------------------|--|--|

| #    | Rects  | DX   | DΥ    | Ratio    | # Rects                 |  |  |

|      |        |      |       |          |                         |  |  |

| 1    | 10803  | 848  | 1073  | 1.27     | 84.23                   |  |  |

| 2    | 11265  | 2072 | 453   | 4.57     | 83.32                   |  |  |

| 3    | 11566  | 840  | 800   | 1.05     | 58.1 <b>0</b>           |  |  |

| 4    | 11853  | 896  | 1088  | 1.21     | 82.24                   |  |  |

| 5    | 11915  | 954  | 856   | 1.11     | 68.54                   |  |  |

| 6    | 12063  | 856  | 910   | 1.06     | 64.54                   |  |  |

| 7    | 12800  | 1155 | 630   | 1.83     | 56.85                   |  |  |

| 8    | 14186  | 900  | 1258  | 1.40     | 79.80                   |  |  |

| 9    | 14423  | 1272 | 657   | 1.94     | 57.94                   |  |  |

| 10   | 15097  | 850  | 1110  | 1.31     | 62.50                   |  |  |

| 11   | 16194  | 1190 | 1106  | 1.08     | 81.20                   |  |  |

| 12   | 17565  | 605  | 1272  | 2.10     | 43.81                   |  |  |

| 13   | 18056  | 1268 | 800   | 1.58     | 56.18                   |  |  |

| 14   | 33387  | 1920 | 963   | 1.99     | 55. <b>38</b>           |  |  |

| 15   | 95901  | 2944 | 1676  | 1.76     | 51.45                   |  |  |

| 16   | 109682 | 3019 | 2370  | 1.27     | 65.23                   |  |  |

Table 5. Data on chip bounding box.

is the average amount of silicon "real estate" devoted to each rectangle, and not the area of each rectangle; the inverse of this figure gives the density of rectangles (in average number of rectangles per  $\lambda^2$  area). This ratio remains remarkably consistent across all chips: the median ratio is 63.5, while the mean is 65.7 (with standard deviation 12.4).

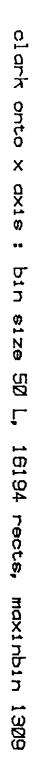

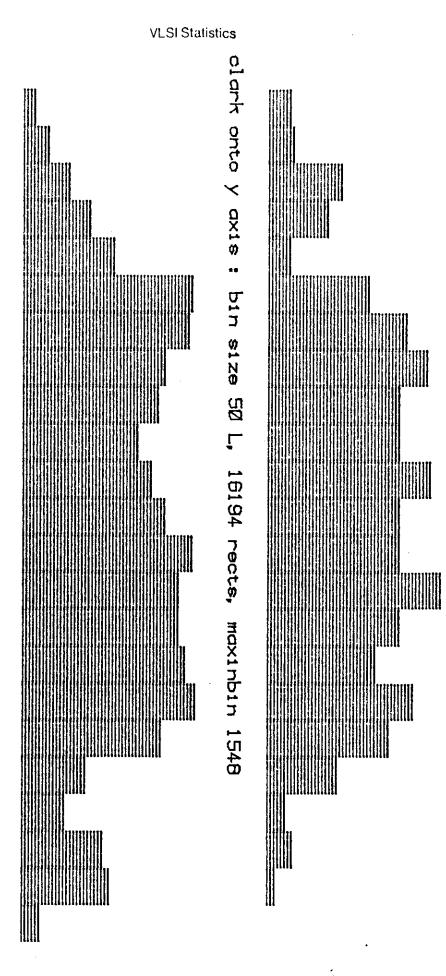

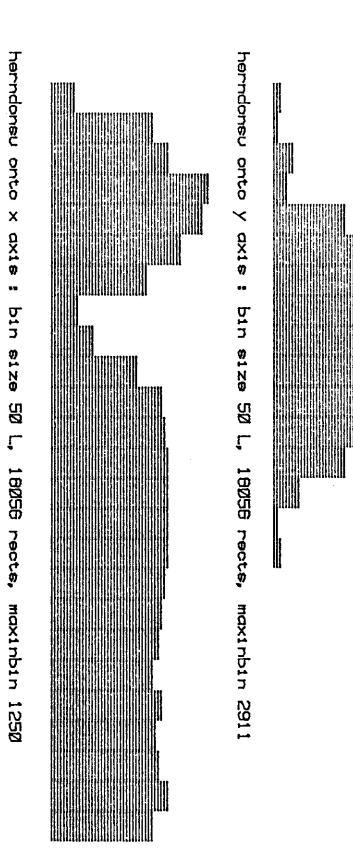

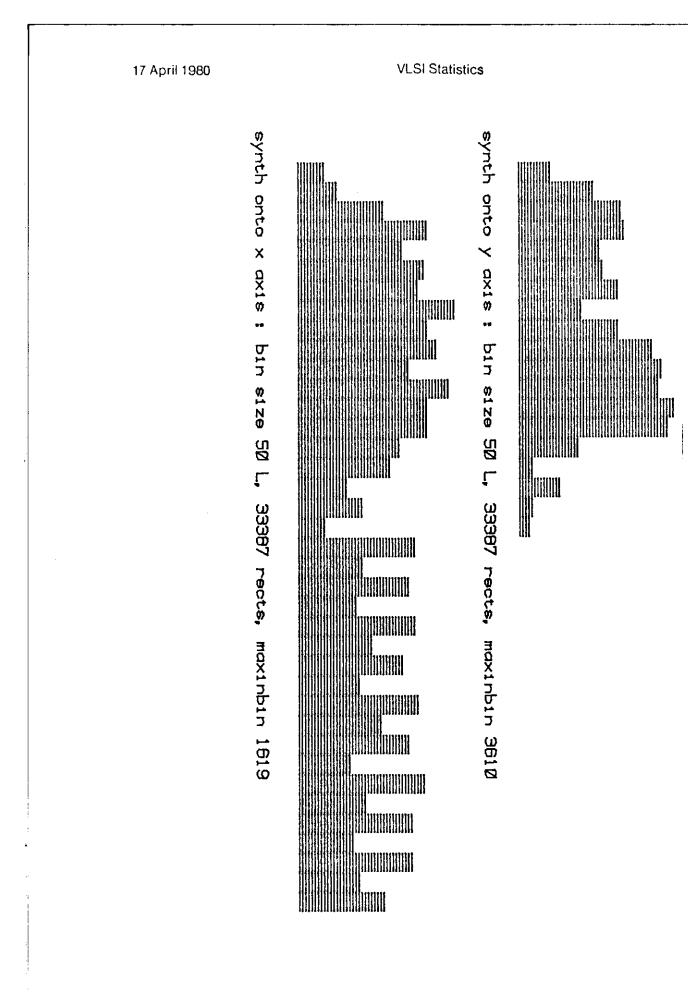

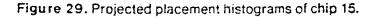

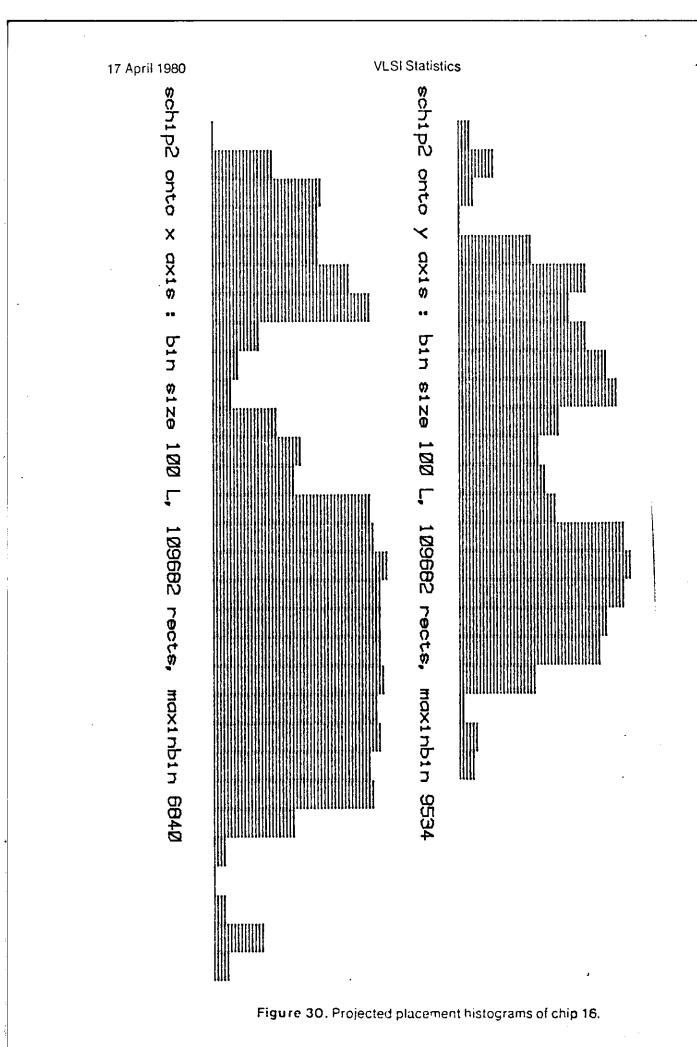

The above discussion shows that the "typical" bounding box containing N rectangles is a square of approximately  $8N^{1/2}\lambda$  on each side. The next subject to investigate is the placement of rectangles over the bounding box: are they spread uniformly over the area, or are they all clustered in a few dense parts of the chip? Histograms in Appendix V show that the rectangles are indeed spread uniformly over (most of) the bounding box.

## 2.4 A Probabilistic Model

The previous sections in this chapter have focussed on a statistical study of existing VLSI chips. For use in analyzing potential algorithms for VLSI tasks, we must condense that data into the more useful form of a probabilistic model. In this section we will study two such models (of many possible): one rather simple and the other somewhat complicated. Before discussing the particular models, though, we must address three topics in a more general context: the shape of the bounding box containing the chips, the placement of the rectangles within the bounding box, and the shape of the individual rectangles.

The first issue that a model of rectangles on chips must face is the bounding box in which the

rectangles are distributed. The aspect ratios of Section 2.3 show that the bounding boxes are approximately square.<sup>5</sup> The ratio of chip area to the number of rectangles shows that the bounding box should have approximately  $64\lambda^2$  area for each rectangle in the set.

The second issue a model must face is the distribution of rectangles over the bounding box. The data of Appendix V shows that the rectangles are indeed uniformly distributed over (most of) the chip's bounding box. This assumption can also be justified by *a priori* arguments based on VLSI design philosophy. One of the aims of a good VLSI design is to make effective use of the silicon area. This implies that the design will fill its bounding box rather uniformly. Although there are typically sparse regions near the edges of the design (containing long wires, bonding pads and pad drivers), the central part of the chip has a much higher (and almost uniform) density of small rectangles that perform most of the computation and data manipulation. The fixed number of layers available for a design (in nMOS there are typically six) and the design practice of not overlapping many rectangles on one layer combine to limit the number of rectangles that cover any given point on the chip; this together with the lower bound on rectangle size implies a constant upper bound on the density of rectangles. Economic arguments provide a lower bound: there is no reason to leave large blank spaces in a design.

The third issue to be faced is the shape of the individual rectangles. Fortunately, we have a great deal of data on rectangle shapes in Section 2.2 and Appendices II through IV.

We can now combine these facts regarding the size and shape of the bounding box, the placement of rectangles, and the shape of rectangles into a probabilistic model. The simplest possible model of an N-rectangle design is that the N rectangles are squares with edge length 7.6 $\lambda$ , uniformly distributed on  $[0, 8N^{1/2}\lambda]^2$ . (The value 7.6 $\lambda$  is from Table 1, and the 8 $\lambda$  is from Table 5.)

On the other hand, we could postulate a much more complex model for generating a set of N rectangles. We first choose an aspect ratio R uniformly from [1,2], and a sparsity S uniformly from [44,84]. (S is the total amount of silicon real estate per rectangle in the bounding box.) We then set the short side of the bounding box to be  $(NS/R)^{1/2}\lambda$ , and the long side to be  $(RNS)^{1/2}\lambda$ . We then distribute the following rectangles uniformly over the bounding box:

• (.72)N components, each with side lengths chosen uniformly on  $[2\lambda, 10\lambda]^2$ . (A more sophisticated method could sample a stored 10-by-10 table giving the probability of realizing each pair of lengths; such a table could be generated from the data in Appendix

<sup>&</sup>lt;sup>5</sup>A number of engineering and economic reasons dictate that the chip's bounding box should be close to square. This often makes wire-bonding easier, and usually makes more efficient use of the package cavity. The authors regret to have to point out that in the designs we studied, there was motivation for "long and skinny" chips: rumors in the design community reported that such designs were more likely to be placed on multiproject chips! Most of their chips with extremely high aspect ratios were very small and therefore filtered by our criterion of examining only chips with at least 10,000 rectangles.

### VLSI Statistics

- 11 -

II.)

.

- (.26)N wires, half vertical and half horizontal, with the short side distributed uniformly between  $2\lambda$  and  $6\lambda$  and the long side distributed exponentially with mean  $40\lambda$  (truncated below  $10\lambda$ ).

- (.02)N other rectangles, for which both edge-lengths are chosen uniformly on [10 $\lambda$ ,Max], where Max is a typical bonding pad edge size (say, 75 $\lambda$ ).

The percentages in the above model are from Table 1, the parameters of each rectangle class are from Tables 2, 3, and 4, and the bounding box distribution is from Table 5.

17 April 1980

# 3. Applications of the Statistics

In this chapter we will consider a set of geometric subproblems that arise in layout, routing and design rule checking called the *geometric intersection problems*. In the abstract problem we are given a set of objects in the plane and must report all pairwise intersections among the objects. In concrete applications the geometric objects are usually components on a chip, and the intersections are potential "trouble areas", such as design rule violations or a place for a crossover.

Much previous work has been done on geometric intersection problems. Baird [1978], Lauther [1978], McCaw [1979], and Wilcox, Rombeek and Caughey [1978] all describe programs for computing geometric intersections that have actually been used in the design of masks. Although all of their programs are much faster than naive geometric intersection programs, they are still slower than desired and lack a solid theoretical basis. Theoretically sound algorithms have been given by Shamos [1978], Bentley and Ottmann [1979] and Bentley and Wood [1980], but they are very complex to code and fail to exploit many of the situations that arise in practice.

In this chapter we will study a particular geometric intersection problem that calls for intersecting rectangles. In Section 3.1 we develop a theoretical algorithm that performs very well for input rectangles drawn from the distributions studied in Chapter 2. Section 3.2 then shows how the theoretical algorithm can be efficiently implemented on the secondary storage media necessitated by the large size of current VLSI designs. We discuss the algorithm's potential for VLSI applications in Section 3.3.

# 3.1 An Algorithm for Finding Rectangle Intersections

In this section we will examine an algorithm for solving the following problem.

The Rectangle Intersection Problem -- Given a set of N rectangles in the plane, each of which has sides parallel to the coordinate axes, report each intersecting pair of rectangles (by calling some procedure).

The operation of intersecting rectangles is fundamental in many VLSI tasks; we will return to these in Section 3.3. A straightforward way of solving the Rectangle Intersection Problem is to compare all  $\binom{N}{2}$  pairs of rectangles. This method is very easy to code and efficient for small values of N, but the O(N<sup>2</sup>) running time is prohibitive for large designs. Bentley and Wood [1980] describe an algorithm for solving the problem in O(N lg N + k) worst-case time, where k is the number of intersecting pairs found. Their algorithm, however, is primarily a theoretical device, being difficult to code and having a large constant factor "hidden" in the O-notation. In this section we will investigate an algorithm that exploits the probabilistic models of Section 2.4 to yield an algorithm with expected running time proportional to N.

The algorithm we will study in this section exploits the probabilistic models of the last chapter to solve the rectangle intersection problem in fast expected time. Before studying that algorithm, it is important for us to summarize the salient points of the probabilistic models *from an algorithmic viewpoint*. The first important fact is the uniformity of the distribution of the rectangles: this uniformity facilitates the use of *bins* to store data. (Bins work very poorly for highly-clustered data, but have excellent performance for uniform distributions). Equally important is the small average edge length of a rectangle (7.6 $\lambda$ ) compared to the average chip width (8N<sup>1/2</sup> $\lambda$ ). We will find these measurements very helpful as we calculate the optimal size of a bin.

The algorithm for reporting all intersections among a set of rectangles is based on a bottom-to-top scan of the set of rectangles. At each time during the scan, all rectangles currently intersecting the horizontal scan line are represented as a set of one-dimensional line segments. When the bottom of a new rectangle is encountered, the rectangles it intersects are found by checking which line segments its segment intersects; its segment is then added to the set. When the top of a rectangle is found, its segment is deleted. In this way, only the rectangles currently intersecting the scan line need be kept "active" at one time, yet all intersecting pairs are correctly reported.

We can now describe the algorithm more precisely. The input is a set of rectangles, each of which is described by a unique name, four real numbers (giving the extreme left, right, bottom and top coordinates), and any other information needed for the VLSI application. The "output" is a call to procedure REPORT for every intersecting pair of rectangles. We will make use of two primary data structures. The EL (for "Event List") sequence contains two entries for each rectangle; one for its bottom edge and one for its top. This list is sorted by y-coordinate, in increasing order. The other data structure is the set of line segments, called SS for "Segment Set", that intersect the hypothetical scan line (we will discuss the implementation of SS later). With this background, the algorithm is described as follows.

#### Algorithm A

- 1. [Build the event list.]

- a. For each rectangle in the input set, create two records in the event list EL: one corresponding to the bottom, one to the top.

- b. Sort EL by increasing y-value. If various rectangles have equal y-values, then place the bottom edges *before* the top edges.

- 2. [Scan through the event list.]

- a. Initialize SS to represent the empty set.

- b. Scan through EL in increasing order by y-value. As each record R in EL is visited, take one of the following actions.

- i. If R represents the bottom of a rectangle, then first check the line segment corresponding to R (that is, the projection of the rectangle onto the x-axis) for intersection with any other segments in SS (reporting all intersecting pairs), and then insert that segment into SS.

The correctness of Algorithm A is based on the fact that if any two rectangles intersect, then they must be "active" (that is, present in SS) at the same time and will therefore be reported in Step 2.b.i.

We will now briefly analyze the time required by Algorithm A. Step 1.a requires O(N) time, and straightforward implementations of the sort in Step 1.b require O(N Ig N) time. We note that the time required to sort can be reduced to O(N) expected time by using the bin method described by Weide [1978]; we will return to the running time of this step in the next section. The initialization cost of Step 2.a is dependent on the implementation of SS, as are the costs of the N insertions and deletions both into and from SS in Steps 2.b.i and 2.b.ii. Our task now is to find an implementation of SS to facilitate rapid insertion and deletion of line segments.

We will implement the SS structure by dividing the portion of the x-axis on which the rectangles fall into a set of *bins*. For instance, if all x-values of rectangles lie between  $0\lambda$  and  $800\lambda$ , then we could have one hundred bins, each of width  $8\lambda$ . The set of bins is implemented in a program as an array of pointers; each pointer points to a linked list of segment names that currently overlap that bin. This situation is illustrated in Figure 1. To insert a new segment into this structure, we merely insert its name into all bins overlapping the segment; to delete it, we traverse the same set of bins and delete the segment name from the linked list of each. To check what segments in SS a new segment X overlaps, we visit each bin in which X falls and compare X against all elements in the bin; careful bookkeeping allows us to be sure that no pair of segments is reported twice.

Figure 1. Segments represented in bins.

The final task we face in the implementation of SS is the specification of exactly how many bins there should be, or alternatively, the width of each bin (for given one, we can determine the other). It is at this point that we make crucial use of the data in Section 2.4: we choose the bin width to be (approximately) the average width of a rectangle, so that each segment is placed in two bins, on the average. By the models in Section 2.4, this implies that each bin has width of approximately  $8\lambda$ , and the total number of bins is the square root of the number of rectangles. In this implementation, the initialization of the bins requires  $O(N^{1/2})$  time; we will shortly show that insertion and deletion have only constant cost on the average. The expected total running time of Stage 2 is therefore O(N).

There is one fact that has yet to be established to prove the above claim of linear running time for Stage 2 of algorithm A. We require that the expected number of rectangles in a bin be a constant

(independent of N), which implies that insertion and deletion have constant cost on the average. The empirical observations of the program's running time to be presented in the next section supports this claim. We can also show that the claim holds under the models of rectangle distribution and size discussed in Section 2.4. Consider first the simple model of an N-rectangle design: the N rectangles are squares with edge length 7.6 $\lambda$ , uniformly distributed on [0, 8N<sup>1/2</sup> $\lambda$ ]<sup>2</sup>; we must determine the expected number of rectangles in SS at any time. The probability that a given square intersects a given scan line is  $(7.6\lambda)/(8N^{1/2}\lambda)$ . (Because the square intersects the scan line defined by y = S if the y value of the lower edge of the square falls within the range [S-7.6 $\lambda$ , S]). The expected number of squares intersecting the scan line at any given time is simply the total number of squares multiplied by the probability that an individual one intersects the scan line, which is  $(7.6\lambda N^{1/2})/(8\lambda)$ , or .95N<sup>1/2</sup>. Each of the N<sup>1/2</sup> bins representing the SS has a width of 8 $\lambda$ ; hence each square is entered into two (or possibly just one) bins. Since the squares are uniformly distributed, the bins are evenly filled and each bin contains approximately two squares; this establishes the claim. Now consider the more complicated model for generating the N rectangles which is based on the trichotomy of components, wires and others. The constant expected number of entries in each bin can be proved in a manner similar to the proof for the simple model above. Of critical importance is that (1) other rectangles have an upper bound on their edge length, and that (2) wires have a constant average length (although the observed distribution does not impose an a priori upper bound on the length of a wire.)

In preparation for the next section we present a quick summary of algorithm A, with a view toward implementation. The first stage consists primarily of a sort, and the second stage is a linear scan through the sorted output of Stage 1. This scan has the pleasant property that it can perform all necessary processing to report intersections using only  $O(N^{1/2})$  storage. Note that the only communication necessary between the two stages of the algorithm is a sequential file giving the sorted event list.

## 3.2 A Pascal Program

In this section we will describe a set of three computer programs that together implement Algorithm A of the last section. Before going into the details of the individual programs, we will first give a brief overview of the system as a whole. The input to the system is a disk file containing the rectangles to be checked for pairwise intersection, and the "output" is a set of calls to a REPORT procedure (which performs some desired operation) reporting each intersecting pair of rectangles exactly once. Algorithm A is divided into two primary stages: Stage 1 creates a sorted "Event List" named EL, and Stage 2 scans through EL. The EL structure is implemented in this system as a (sorted) disk file. With this overview in mind, we can now describe the computer implementations of the two stages of the algorithm.

The purpose of Stage 1 is to create the EL file and then sort it. In the first substep (Step 1.a), a simple (40 line) Pascal program creates an unsorted version of the EL file by representing each rectangle in the input file twice: once for the bottom edge and once for the top. The records of this file are then sorted into increasing order by y-coordinate, with a secondary sort key chosen so that events representing bottom edges precede top edges for equal y-values. The sorting program to accomplish this in our system is a standard system sorting program. As mentioned in Section 3.1, we could use a linear expected-time sort based on bins (see Weide [1978]) but this would have been much more difficult to code. On the other hand, it is possible to avoid an explicit sort altogether by generating the rectangles in sorted order from the CIF hierarchical description: at any time, the symbol with the lowest bounding box is expanded first.

The second stage of Algorithm A scans through the sorted event list, performing operations on the segment structure SS. The Pascal program implementing this scan contains about 400 lines of code, of which only 220 are for the algorithm itself, while the remaining 180 are for testing and timing. The number of bins in SS was chosen to be equal to the square root of the number of rectangles, that is,  $N^{1/2}$ . By the data of Chapter 2, this implies an average bin width of approximately 8 $\lambda$ .

Extensive measurements of the time and space usage of the program were performed. The program corresponding to Step 1.a of the algorithm was I/O bound. Step 1.b was a standard system sort, which has been studied in great detail elsewhere (see, for example, Knuth [1973, Section 5.4]). We therefore concentrated our measurements on the time and space requirements of Stage 2 of the program.

The performance of the program implementing Stage 2 is summarized in Table 6. The Pascal programs were run on a DEC PDP-KL10 (ARPANET Host CMU-10A). The programs were executed on VLSI designs from recent Xerox PARC multiproject chips that contain between 4,000 and 12,000 rectangles.<sup>6</sup> The first row of the table describes the performance of the program on a chip containing 4689 rectangles. There were 219 elements in the segment set SS on the average, and SS was never larger than 475. The ratio of the maximum size of SS to the root of the number of rectangles is 6.94. The running time of the program was 8.9 seconds, and the amortized time per rectangle is 1.9 milliseconds. The number of rectangle intersections found was 14441, and the ratio of the chip's width to its height was 3.1.

As predicted, the running time of the program implementing Stage 2 of our algorithm is proportional to N: the time per rectangle is between 1.73 and 1.93 milliseconds. The rectangle sets used for these measurements include features from all layers of a chip design. Hence an average

<sup>&</sup>lt;sup>6</sup>For historical reasons (the transfer of VLSI computing at CMU from a PDP-10 to a VAX-11-780), we report the running time of our programs on a set of earlier (and smaller) multiproject chip designs.

VLSI Statistics

| ∦ Rects<br>(= N) | Segment Set Size<br>Mean Max Max/N <sup>1/</sup> |     | iet Size<br>Max/N <sup>1/2</sup> | Time<br>(sec) | Time/N<br>(msec) | # Ints | Aspect Ratio<br>(Hor/Vert) |

|------------------|--------------------------------------------------|-----|----------------------------------|---------------|------------------|--------|----------------------------|

| 4689             | 219                                              | 475 | 6.94                             | 8.9           | 1.9              | 14441  | 3.1                        |

| 4960             | 86                                               | 172 | 2.44                             | 8.6           | 1.73             | 11783  | 1.3                        |

| 5272             | 111                                              | 246 | 3.39                             | 9.3           | 1.76             | 14441  | 1.5                        |

| 7176             | 150                                              | 359 | 4.24                             | 12.9          | 1.89             | 18949  | 1.3                        |

| 7416             | 123                                              | 254 | 2.95                             | 14.3          | 1.93             | 22166  | .73                        |

| 11316            | 55.8                                             | 124 | 1.17                             | 20.7          | 1.83             | 30565  | .22                        |

Table 6. Measurements for Stage 2 of Algorithm A.

rectangle intersects a relatively large number of other rectangles; in our case this number lies between 3.5 and 6. Many applications need intersections of rectangles only from a subset of the chip layers, and the algorithm will perform even better in that case: the number of intersections per rectangle will be lower, and the SS can be searched more rapidly.

The total number of memory words used in Stage 2 is proportional to the number of bins plus the *maximum* number of rectangles ever in SS at one time. The fourth column of Table 6 shows that this is bounded above by approximately  $4RN^{1/2}$  in practice, where R is the aspect ratio of the chip. (The simple probabilistic model of Section 2.4 predicts  $RN^{1/2}$ ; the observed increase is due to the local clustering in real designs not accounted for in our model.) This has a very pleasant implication for the main memory utilization of the algorithm: note that if N is one million and the aspect ratio is unity, then at most four thousand rectangles are ever present in main memory at the same time!

Our program was designed to scan the chip from its bottom to its top, and this led to severe space inefficiency for chips that were "short and fat". Because the rectangles are distributed uniformly over the chip, the number of rectangles intersecting the scan line will be proportional to the line's length, which is less if the chip is scanned in the "tall and skinny direction". (Note that the length of the scan line is less by a factor of the square of the aspect ratio.) Recall that the space used by the algorithm is directly proportional to the number of rectangles intersecting the scan line. This analysis, together with the data of Table 6, suggests strongly that design rule checkers should be designed to "rotate" their inputs, so the chips are always scanned in the beneficial direction.

## 3.3 Applications in VLSI Tasks

VLSI technology will soon allow several hundred thousand devices in a single IC design. The lowest common denominator for these designs is the geometric specification of the shapes on the mask layers. *Design rule checking* is the process of determining whether certain interrelationships are maintained between those shapes; for example, whether all unrelated polysilicon and diffusion lines are separated by at least  $1\lambda$ . Design rule checking programs are the "syntax checkers" of the IC

world -- they guarantee that the form of the chip is correct (but not, of course, that it does what the designer intended).

Algorithm A of Section 3.1 can be used in design rule checking. Most minimum width, minimum clearance, and enclosure checks can be performed by the combination of programs to expand/shrink rectangles, perform logical operations (for example, forming the logical OR of two layers to produce a third), and an intersection reporter. Such systems are essentially batch oriented; an entire design file is checked at once and all design rule violations reported. The fast rectangle intersector is the workhorse here, processing a large number of rectangles in a single pass. Note that the time required by the rectangle intersector is linear in the number of rectangles, and its space requirements are proportional to the square root of the number of rectangles.<sup>7</sup>

While batch-oriented geometric design rule checkers are in wide use, interactive systems can provide valuable feedback as designs are entered. In an operator-guided placement and routing system, violations can be automatically flagged as each cell is placed. It may also be possible to hide a considerable amount of computation in the operator's "think" time. Straightforward extensions of the algorithm above make such *incremental* checks easy. The chip can be divided into two-dimensional bins, where a rectangle is put into all the bins it overlaps. Once these bins have been constructed, it is simple to find which existing rectangles intersect a given new rectangle. The data of Chapter 2 and Appendix V ensures that this approach will be very fast: the shape data tells us that rectangles are small (and will therefore fall into few bins), and the uniformity of the placement data tells us that only relatively few rectangles will fall into any particular bin.

- 18 -

<sup>&</sup>lt;sup>7</sup>As appealing as a fast geometric design rule checker may be, we believe that faster design rule checkers will take advantage of the high-level information in hierarchical IC designs. Such designs consist of cells that implement a particular function, connected logether by some amount of wiring. Each cell in turn consists of an agglomeration of cells, components, and wires; the lowest-level cells are merely collections of components and wires. Performance improvements may be achieved by taking advantage of the structure in the design. For instance, it is necessary to check any particular cell only once -- subsequent placements of the cell need be checked only if they overlap other shapes. By intersecting the bounding box of a cell before "exploding" the cell into its constituent parts, a quick yes/no determination can be made of whether anything within the cell might intersect previously placed cells. A single intersection check can therefore eliminate many rectangles from consideration. The fast intersection algorithm might be useful for such geometric manipulations.

VLSI Statistics

# 4. Conclusions

There are two main contributions in the work of the previous chapters. The first contribution is the program for finding geometric intersections: it is easily coded, very fast, and space-efficient. Preliminary comparisons indicate that it is much faster than previous programs for similar tasks. The second, and more fundamental, contribution of this work is the data on the distribution of chip components and the methodology for using such data to design fast programs. We feel that the techniques we have used here will prove to be of broad applicability in constructing design aids for VLSI systems.

A great deal of further work remains to be done. The algorithm of Chapter 3 is being used in a design rule checker currently under development at Carnegie-Mellon. An important open problem is to gather more data on VLSI designs: two particularly interesting questions are whether the conclusions we drew from this data will "scale up" to designs an order-of-magnitude larger, and how our data will compare with industrial chips (as opposed to the Mead-Conway style designs). An interesting problem in VLSI design is to employ more knowledge than the strictly geometric issues that we have studied here; it is therefore important to study the hierarchical structure inherent in the CIF representation of a VLSI design.

### Acknowledgements

We are grateful to the chip designers mentioned in Appendix I for allowing their designs to be used in this study, and to Bill Eddy and Bob Sproull for their helpful comments.

- 19 -

VLSI Statistics

# References

- Baird, H. S. [1978]. "Fast algorithms for LSI artwork analysis," Journal of Design Automation and Fault-Tolerant Computing 2, 2, pp. 179-209.

- Bechtolsheim, A. and T. Gross [1980], "A Parallel Search Table for Logarithmic Arithmetic," paper presented at the M.I.T. Conference on Advanced Research in Integrated Circuits, January, 1980.

- Bentley, J.L. and T. Ottmann [1979]. "Algorithms for reporting and counting geometric intersections," *IEEE Transactions on Computers C-28*, 9, pp. 643-647, September 1979:

- Bentley, J. L. and D. Wood [1980]. "An optimal worst-case algorithm for reporting intersections of rectangles," to appear in *IEEE Transactions on Computers*.

- Conway, L., A. Bell, M. Newell, R. Lyon, and R. Pasco [1980]. Implementation Documentation for the MPC79 Multi-University Multiproject Chip-Set, Xerox PARC Report, January 1980.

- Clark, J.H. [1980], "A VLSt Geometry Engine for Computer Graphics," paper presented at the M.I.T. Conference on Advanced Research in Integrated Circuits, January, 1980.

- Conway, L., A. Bell, M. Newell, R. Lyon, and R. Pasco [1980], "Implementation Documentation for the MPC79 Multi-University Multiproject Chip-Set," Xerox PARC Report, January, 1980.

- Holloway, J., G. Steele, G.J. Sussman, and A. Bell [1980], "The SCHEME-79 Chip," paper presented at the M.I.T. Conference on Advanced Research in Integrated Circuits, January, 1980.

- Hon, R. W. and C. H. Sequin [1980]. A Guide to LSI Implementation, 2nd edition, Xerox PARC TR SSL 79-7, Chapter 7, January 1980.

- Lauther, U. [1978]. "4-dimensional binary search trees as a means to speed up associative searches in design rule verification of integrated circuits," *Journal of Design Automation and Fault-Tolerant Computing* 2, 3, pp. 241-247.

- McCaw, C. R. [1979]. "Unified shapes checker -- a checking tool for LSI," Proceedings of the Sixteenth Design Automation Conference, pp. 81-87, June 1979, ACM.

- Mead, C. A. and L. Conway [1980]. Introduction to VLSI Systems. Addison-Wesley, Reading, MA., 1980.

- Shamos. M. I. [1978]. "Problems in computational geometry," unpublished Ph.D. Thesis, Yale University, 1978.

- Weide, B. W. [1978]. "Statistical methods in algorithm design and analysis", Ph.D. Thesis, Carnegie-Mellon University, August 1978.

- Wilcox, P., H. Rombeek, and D. M. Caughey [1978]. "Design rule verification based on one dimensional scans", Proceedings of the Fifteenth Design Automation Conference, June 1978, ACM.

VLSI Statistics

# I. Description of the Chips

Most of the following chips were designed as part of a VLSI course given at Stanford University by Rob Mathews and John Newkirk. The designs were implemented on a multiproject chip (MPC79) managed by Xerox PARC, with data communication provided by the ARPANET, masks by Micro Mask, Inc., and wafer fabrication by Hewlett-Packard. (For more details see Conway et. al. [1980].) In several cases, papers are available that describe the design in detail. Four of the projects have not yet been implemented, as they were not completed by the final MPC79 deadline. Those projects will probably be implemented on future multiproject chips.

1. Bill Frolik and Roderick Young -- Digital Timer.

- 2. Rob Mathews and John Newkirk -- Firecode Chip.

- 3. Huang -- Not implemented.

4. Forest Baskett -- Ethernet Synchronizer.

5. Marc Hannah and Peter Eichenberger -- Rectangle Generator.

- 6. Mike Tarsi and Nagatsugu Yamanouchi -- Multifunction Digital Clock.

- 7. David Noice and Neil Midkiff -- Multiplier/Divider.

- 8. Sytwu -- Not implemented.

- 9. Gluss -- Not implemented.

- 10. Redford -- Not implemented.

- 11. Jim Clark -- Graphics ALU (see Clark [1980]).

- 12. Andy Bechtolsheim and Thomas Gross -- Parallel Search Table for Log Arithmetic (see Bechtolsheim and Gross [1980]).

- 13. Matt Herndon and Jeff Thorson -- Typesetting Machine.

- 14. Synth -- Part of a digital speech synthesizer designed by Jim Cherry of MIT.

- 15. Filters -- Part of a speech recognition system designed by Dick Lyon at Xerox PARC.

- 16. SChip2 -- The second version of a Lisp microprocessor designed by Sussman, Steele, and Holloway from MIT and Bell from Xerox PARC (see Holloway, et. al. [1980]).

- 21 -

## VLSI Statistics

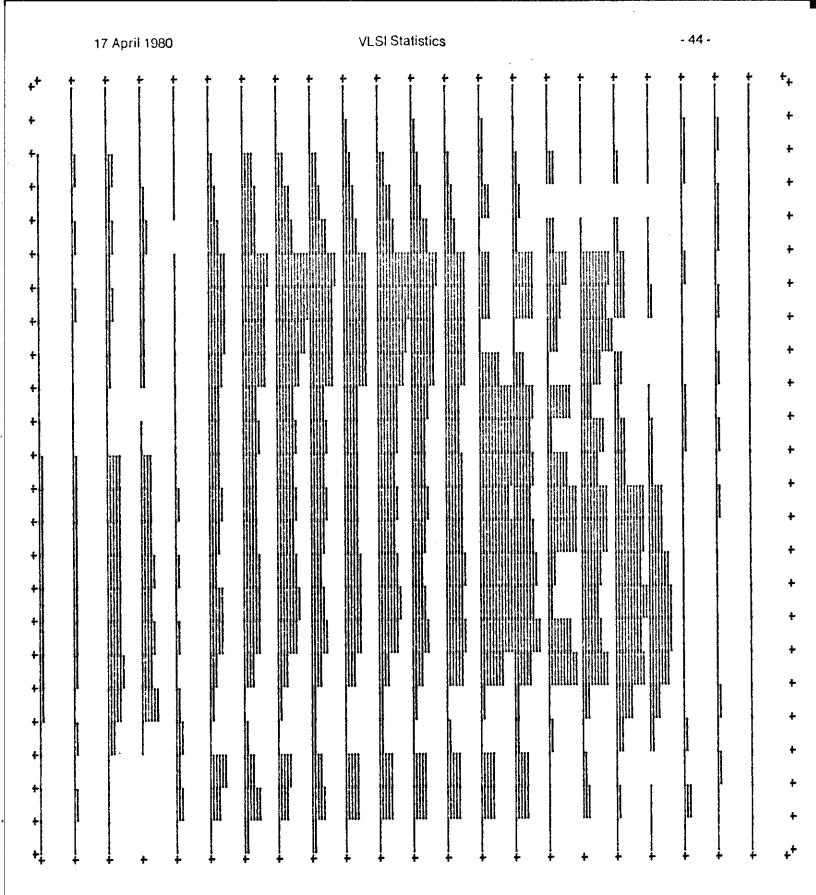

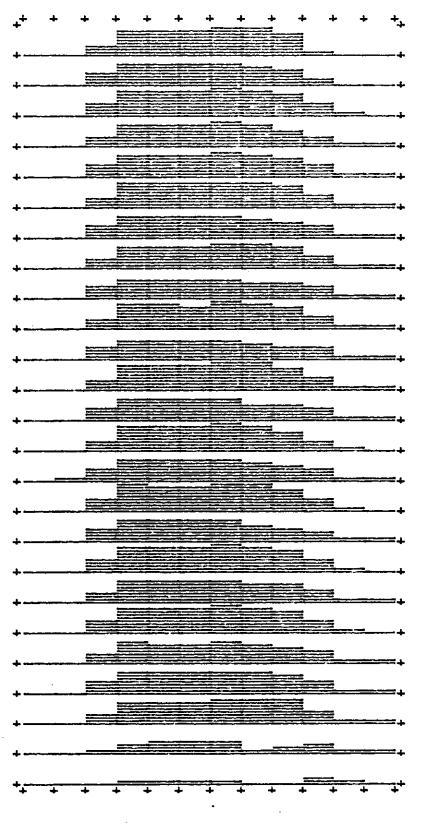

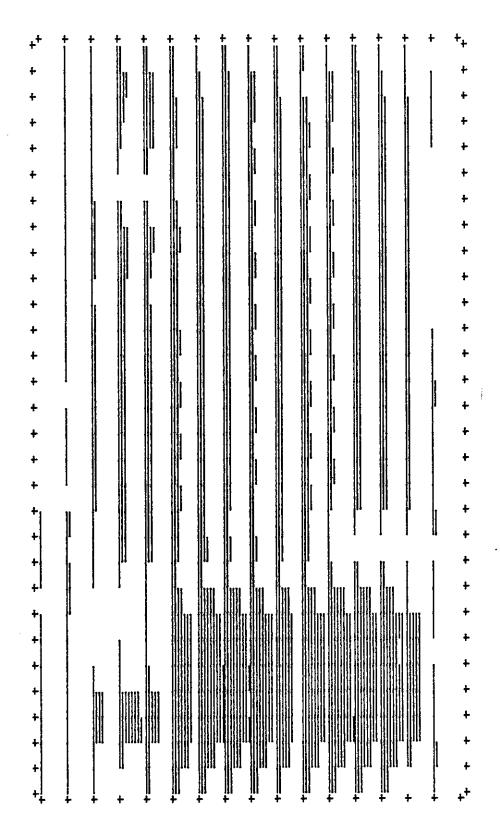

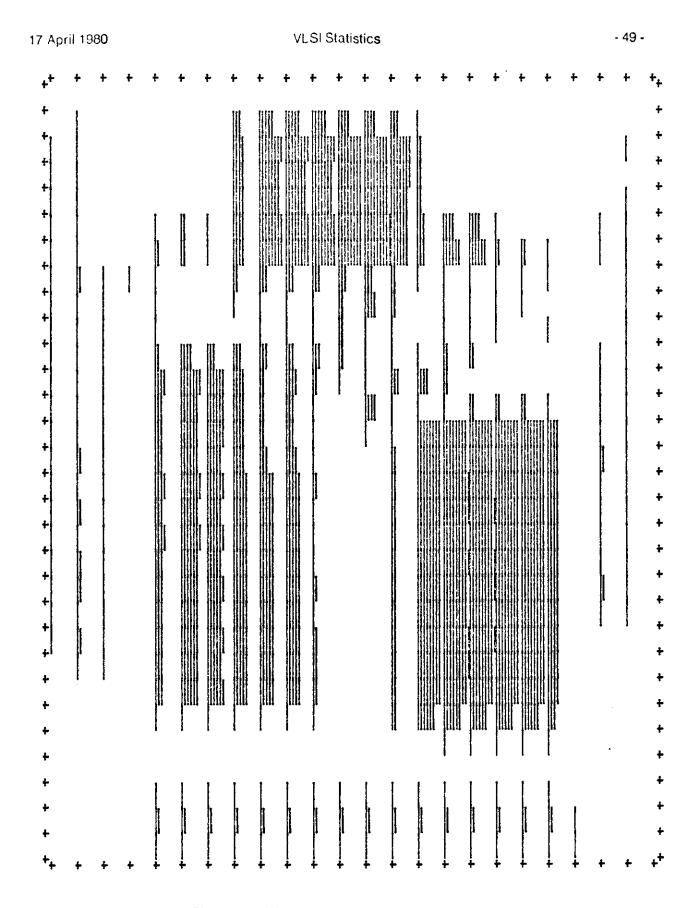

# II. Component Histograms

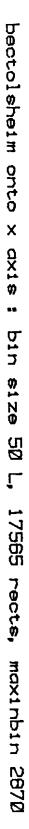

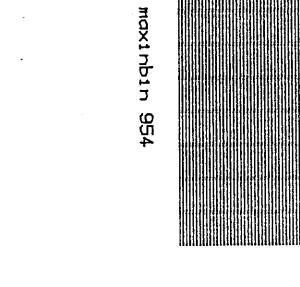

In this appendix we will present histograms that give more detail on the distribution of components. The histograms are contained in Figures 1 through 6; they describe chips 11 through 16, respectively. Figure 1 describes chip 11. The first three lines of that figure summarize data from Table 2 of Section 2.2.2. The next part of the figure gives a two-dimensional histogram of the component distribution. For instance, there were  $1059 2\lambda$ -by- $4\lambda$  components (that is,  $2\lambda$  wide by  $4\lambda$  high). The five x's in that box indicate that these 1059 components are approximately half the number of the maximum number of components in any of the one hundred sizes (that is, the  $2125 4\lambda$ -by- $4\lambda$  components, which have ten x's). The final thirteen lines in the figure "linearize" this two-dimensional data by summarizing the longest edge of the components. For instance, 2139 components had a longest edge of exactly  $6\lambda$  (or 19.2% of all components), and 81.2% of the components had both edges less than or equal to  $6\lambda$  in length.

A number of facts are readily apparent from these tables. The first is that there are few components that have an edge length of 1 $\lambda$ . Since a 1 $\lambda$  edge violates Mead and Conway's design rules, all such components were in fact part of logos. The second obvious fact is that most components were  $2\lambda$ -by- $2\lambda$ ,  $2\lambda$ -by- $4\lambda$ ,  $4\lambda$ -by- $4\lambda$ , or  $4\lambda$ -by- $6\lambda$  (or rotations of those by 90°). Finally, we note that most component edge lengths were less than or equal to  $6\lambda$ . From the summaries at the bottom of the figures, we see that on all chips, 78% or more of the components had longest edge less than or equal to  $6\lambda$ . Of the remaining 22% with one edge greater than  $6\lambda$ , very few had both edges greater than  $6\lambda$  (observe that the upper right  $4\lambda$ -by- $4\lambda$  rectangle of each histogram is very sparsely populated). This implies that even if we had changed our definition of component to all rectangles with both edges less than or equal to  $6\lambda$ , our results would have changed little.

- 22 -

| 17 A | pril 19               | 80                         |                          |                |                          | VLSI             | Statistic                | s        |              |          |                 | - 2      | 3 -     |

|------|-----------------------|----------------------------|--------------------------|----------------|--------------------------|------------------|--------------------------|----------|--------------|----------|-----------------|----------|---------|

| 111  | 128 c                 | rectan<br>compon<br>ent ed | ents                     | (6<br>eng      | 8.7% (<br>th :           | of tot<br>Mean 4 | al)<br>.0, S             | tanda    | ard          | deviat   | ion 2.0         | •        | • .     |

| Dis  | strib                 | oution                     | of                       | com            | ponen <sup>.</sup>       | t size           | S                        |          |              |          |                 |          |         |

|      | 10                    |                            | 1                        | x<br>32        | x<br>1                   | x<br>31          |                          |          | х<br>12      | x<br>1   |                 |          | x<br>1  |

|      | 9                     |                            | · 1                      | <b>x</b><br>76 |                          | <b>x</b><br>86   |                          |          | x<br>16      | •        |                 | x<br>2   |         |

|      | 8                     |                            |                          | x<br>48        | х<br>З                   | x<br>116         |                          | ŝ        | x<br>314     |          | x<br>3          | ·        |         |

|      | 7                     |                            | 1                        | x<br>33        | X<br>7                   | x<br>14<br>x     |                          |          | x<br>4       | x<br>23  |                 |          |         |

|      | 6                     |                            | 2                        | x<br>99        | x<br>2                   | xx<br>558        |                          | x<br>3 ( | x<br>311     | x<br>7   | <b>x</b><br>133 | ×<br>28  | x<br>15 |

|      | 5                     | -                          |                          | x<br>71<br>xx  | x<br>2<br>x              | x<br>40<br>xxxxx | 3                        | ×<br>1   | x<br>16<br>x |          |                 |          |         |

|      | 4                     |                            |                          | хx             |                          | xxxxx<br>2125    |                          | x<br>3 ( | xx<br>525    | x<br>36  | x<br>38         | x<br>77  | x<br>12 |

|      | 3                     |                            | ×x                       | x<br>22<br>x x | x<br>40                  | x<br>295<br>xx   |                          | x<br>3   | x<br>1       | х<br>6   | x<br>1          | x<br>2   | x<br>1  |

|      | 2                     |                            | x x<br>17                | хx             | ×<br>47                  | x x<br>790       |                          | x<br>4 : | x<br>301     | x<br>146 | <b>x</b><br>96  | x<br>307 | x<br>64 |

|      | 1                     |                            |                          | х<br>32        |                          |                  |                          |          |              |          |                 |          |         |

|      | -                     | 1                          | <b></b> .                | 2              | 3                        | 4                |                          | 5        | 6            | 7        | 8               | 9        | 10      |

| Loi  | npone<br>ngest<br>dge | ent si<br>t                |                          | rea<br>oun     |                          | Cumula           | tive                     |          |              |          |                 |          |         |

|      | 1<br>2<br>3<br>4      |                            | 0<br>739<br>109          | 15<br>1        | .0%<br>.6%<br>.0%        | 15<br>16         | .0%<br>.6%<br>.6%        |          |              |          | ·               |          |         |

|      | 4<br>5<br>6<br>7      |                            | 600<br>449<br>139<br>376 | 4<br>19        | .3%<br>.0%<br>.2%<br>.4% | 62<br>81         | .9%<br>.0%<br>.2%<br>.6% |          |              | ·        |                 |          |         |

| J    | 8<br>9<br>10          |                            | 752<br>694<br>270        | 6<br>6         | .8%<br>.2%<br>.4%        | 91<br>97         | .3%<br>.6%<br>.0%        |          |              |          |                 |          |         |

Figure 1. Components of chip 11.

| 17 April 19              | 80                                 |                    |                | VLSI Sta            | atistics    |           |         |         | - 24      | 4 -            |

|--------------------------|------------------------------------|--------------------|----------------|---------------------|-------------|-----------|---------|---------|-----------|----------------|

| 10219 c                  | rectangle<br>component<br>ent edge | s (58.             | .2% o<br>n : M | f total<br>lean 3.5 | )<br>, Stan | dard      | deviati | on 1.6  |           |                |

| Distrit                  | oution of                          | comp               | onent          | sizes               |             |           |         |         |           |                |

| 10                       |                                    | x<br>4,4           |                | x<br>24             |             |           |         |         |           |                |

| 9                        |                                    | x<br>1             |                | x<br>10             |             | x<br>20   | ·       | •       |           |                |

| 8                        |                                    | x<br>5             |                | x<br>11             |             | - x<br>36 |         | x<br>20 |           |                |

| 7                        |                                    | x<br>68            |                | x<br>66             |             |           |         |         |           | <b>x</b><br>66 |

| 6                        |                                    | x<br>23            | x<br>1         | x<br>292            | x<br>22     | x<br>2    |         | x<br>26 | x<br>11 - |                |

| 5                        |                                    | x<br>86<br>x       | x<br>2         | x<br>1<br>xxxxx     | x<br>4      | x<br>20   |         |         |           |                |

| 4                        |                                    | xx<br>962          | x<br>233       | xxxxx<br>3138       | . x<br>12   | x<br>222  |         | x<br>90 |           | x<br>10        |

| 3                        |                                    | <b>x</b><br>6<br>1 | x<br>17        | x<br>177<br>xx      | x<br>11     | x<br>11   | x<br>3  |         | Х<br>4 .  | x<br>2         |

| 2                        | . ×                                | xxx<br>583         | x<br>115       | xx<br>1193          | x<br>60     | x<br>134  | x<br>97 | x<br>88 | ×<br>44   | x<br>143       |

| 1                        |                                    | x<br>2             |                |                     |             |           |         |         |           |                |

|                          | 1                                  | 2                  | 3              | 4                   | 5           | 6         | 7       | 8       | 9         | 10             |

| Compon<br>Longes<br>edge | ent size<br>t                      | break<br>Count     | down           | Cumulat             | ive         |           |         |         |           |                |

| 1                        | (<br>2586                          |                    | 0%<br>3%       | 0.<br>25.           |             |           |         |         |           |                |

| · 2<br>3<br>4<br>5<br>6  | 138<br>5703                        | 31.                | 4%             | 26.<br>82.          | 7%          |           |         |         |           |                |

| 5                        | 176                                | 51.                | 7%<br>1%       | 84.<br>91.          | 2%          |           |         |         |           |                |

| 7                        | 234                                | 42.                | 3% `           | 93.                 | 6%          |           |         |         |           |                |

| 8                        | 270                                | 0.                 | 7%<br>9%       | 96.<br>97.          | 2%          |           |         |         |           |                |

| 10                       | 289                                | 9 Z.               | 8%             | 100.                | U /a        | •         |         |         |           | و              |

Figure 2. Components of chip 12.

9

10

221

603

1.6%

4.4%

### VLSI Statistics

18056 rectangles 13731 components (76.0% of total) Component edge length : Mean 3.9, Standard deviation 1.8

Distribution of component sizes

|                            |              | or com          | Juneni     | 5 3 1 2 6 3     |          |                |          |                 |                   |                 |

|----------------------------|--------------|-----------------|------------|-----------------|----------|----------------|----------|-----------------|-------------------|-----------------|

| 10                         |              | <b>x</b><br>295 |            | x<br>4          |          | x<br>128       |          |                 |                   |                 |

| 9                          |              | x<br>44         |            | x<br>2          |          | <b>x</b><br>90 |          |                 |                   |                 |

| 8                          |              | <b>x</b><br>74  |            | x<br>18         |          | x<br>233       |          |                 |                   |                 |

| 7                          |              | x<br>303        |            | x<br>1          |          |                |          |                 |                   |                 |